| Design For Low Power holistic |                                                                                              |            |                                |                                                                   |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------|------------|--------------------------------|-------------------------------------------------------------------|--|--|

|                               | Constant<br>Throughput/Latency                                                               |            | Variable<br>Throughput/Latency |                                                                   |  |  |

|                               | Design Time                                                                                  | Non-Active | Modules                        | Run Time                                                          |  |  |

| Dynamic<br>& Short<br>Circuit | Logic<br>Re-Structuring,<br>Logic 5: Xig<br>Reduced V <sub>DD</sub><br>Multi-V <sub>DD</sub> | Cioc       | ating                          | Dynamic or<br>Adaptive<br>Fr <b>2445X</b> &<br>Voltage<br>Scaling |  |  |

| Leakage                       |                                                                                              | Sleep Tra  |                                | 2X-10X                                                            |  |  |

|                               |                                                                                              |            | Source                         | z: J. Rabaey, UCB 2005                                            |  |  |

2

3

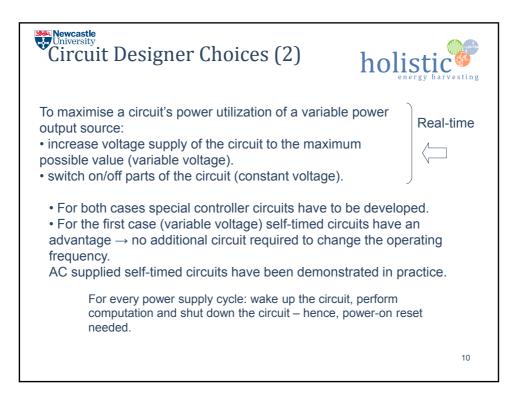

| Circuit Designer Choices (1) |                                                                                                                                                                                                                                  |  |  |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

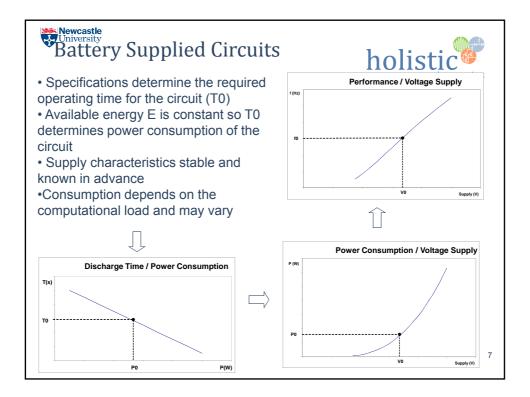

| Battery ⊟<br>Supply          | <ul> <li>Determine from T0 the required power consumption P0.</li> <li>Design the circuit for constant P0 consumption → constant V0 supply → constant f0 performance (or apply DVS and DVFS to maximise battery life)</li> </ul> |  |  |  |  |

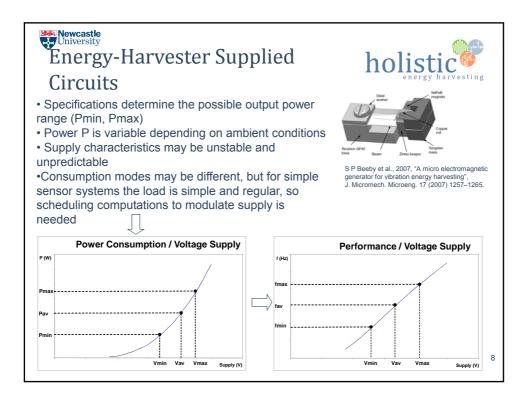

| Energy-Harvester<br>Supply   | <ul> <li>Design the circuit for constant Pmin consumption         <ul> <li>→ constant Vmin supply → constant fmin             performance.</li></ul></li></ul>                                                                   |  |  |  |  |

|                              | <ul> <li>Track available power Paverage → change circuit consumption/performance in real-time → faverage &gt; fmin.</li> </ul>                                                                                                   |  |  |  |  |

|                              | 9                                                                                                                                                                                                                                |  |  |  |  |