Low Frequency Noise Analysis of Monolithically Fabricated 4H-SiC CMOS Field Effect Transistors

Low Frequency Noise Analysis of Monolithically Fabricated 4H-SiC CMOS Field Effect Transistors

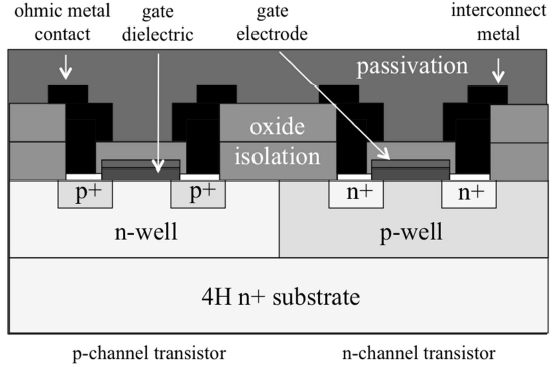

Low frequency noise in 4H-SiC lateral p-channel metal oxide semiconductor field effect transistors (PMOSFETs) in the frequency range from 1 Hz to 100 kHz has been used to investigate the relationship between gate dielectric fabrication techniques and the resulting density of interface traps at the semiconductor-dielectric interface in order to examine the impact on device performance. The results show that the low frequency noise characteristics in p-channel 4H-SiC MOSFETs in weak inversion are in agreement with the McWhorter model and are dominated by the interaction of channel carriers with interface traps at the gate dielectric/semiconductor interface.

Go back